# Real Time Operating System design for Multiprocessor system-on-a-chip

Tesi per il consegumento del diploma di perfezionamento

Anno Accademico 2004/2005

Paolo Gai (pj@sssup.it)

Collegio dei docenti

Prof. Giorgio C. Buttazzo

Prof. Paolo Ancilotti

Prof. Marco Di Natale

Ing. Giuseppe Lipari

**RETIS** Lab, Scuola Superiore S. Anna, Piazza Martiri della Libertà 56100 Pisa - Italy

to Giorgio and Assunta.

### Acknowledgements

This thesis describes some research I have done during this PhD, that is a little thing compared to the many things I did in the same period of time (included many silly photos and dinners and ...). I always thought that this page of my thesis would be probably the most difficult to write (and in fact it has been the last one I wrote!), because many are the friends that I should thank, little the space I have in a single page, and still little my knowledge of the English language to cite them in the appropriate way. In any case, let me try:

First of all, Beatrice, that really supported me during these years.

Then, my supervisors *Giuseppe, Marco, Paolo, Giorgio and Luigi*: I really would like to thank them, for their friendship and for their advice. *Alberto*, that has been the light for many inspirations, tolerant in many occasions and of course a good fiend. *Lui*, that convinced me to start this journey, and *Sanjoy*, who always surprised me for his elegance in research and life.

Then, *Tomas*, good friend from the icy Sweden, *Peter*, *Gerhard*, *Radu*, *Damir*, *Paulo*, *Luis*, *Lucia*, *Giancarlo*, *Roberto*, *Rodrigo*, *Anton*, *Shelby*, *Alan*, *Guillem*, *Ian*, *Julio*, *Mario*, *Michael*, *Tullio*, *Nino*, *Clara*, *John*, *Joan*, *Bjorn*, *Jakob*, and many other friends I met jumping around universities and conferences.

After that, people I worked with since a while in Magneti Marelli, *Walter*, *Giovanni*, *Paolo*, *Claudio*, *Enrico*, *Giacomo*, and others, who gave me the opportunity to work on the Janus architecture.

And, last but not least, all the ReTiS Lab and the PSV (in random order): *Paolo* (together again after a long time), *Nicola, Francesco, Alessandro, Marko, Giacomo, Shiva, Davide, Igor, Luca, Gerardo, Tonino, Claudio, Marco, Gianluca, Bruno, Sachin, Simonetta, Mara, Michael, Rodolfo* (that highlighted some bugs in my proofs), *Enrico, Gabriele, Chiara, Antonio, Elisabetta, Fabrizio, Barbara, Giampiero, Mario, Michele, Bruno,* and of course all the other people that I should have cited but I just forgot...

PJ

# Summary

The primary goal for real-time kernel software for single and multiple-processor on a chip is to support the design of timely and cost-effective systems. The kernel must provide time guarantees, in order to predict the timely behavior of the application, an extremely fast response time, in order not to waste computing power other than the application cycles and save as much RAM as possible in order to reduce the overall cost of the chip.

The research on real-time software systems has produced algorithms that allow to effectively schedule system resources while guaranteeing the deadlines of the application and to group tasks in a very short number of non-preemptive sets which require much less RAM memory for stack. Unfortunately, up to now, the research focus has been on time guarantees rather than the optimization of memory usage. Furthermore, these techniques do not apply to multiprocessor architectures which are likely to be widely used in future microcontrollers.

This thesis presents innovative scheduling and optimization algorithms, which solve the problem of guaranteeing schedulability with an extremely short operating system overhead and minimizing RAM usage.

I developed a fast and simple algorithm for sharing resources in homogeneous multiprocessor systems, together with an innovative procedure for assigning a preemption threshold to tasks. When used in conjunction with a preemption threshold assignment algorithm, the algorithm further reduces the RAM usage in multiprocessor systems.

Finally, I discuss the problem of multiprocessor scheduling for asymmetric architectures composed by a general purpose CPU and a DSP. The challenging issue addressed in this part is to verify whether the use of a dedicated processor can effectively enhance the performance of an embedded system still maintaining some kind of real-time guarantee. In particular, I provide a method for increasing the schedulability bound both for fixed and dynamic scheduling, allowing a more efficient use of the computational resources.

# Contents

| 1 | Intr | oductio  | n           |                                                 | 17 |

|---|------|----------|-------------|-------------------------------------------------|----|

|   | 1.1  | Why n    | nultiproces | ssors?                                          | 19 |

|   | 1.2  | Saving   | g RAM spa   |                                                 | 21 |

|   | 1.3  | Thesis   | contributi  | ons                                             | 21 |

|   | 1.4  | Thesis   | outline .   |                                                 | 22 |

| 2 | Bac  | kgroun   | d           |                                                 | 23 |

|   | 2.1  | Refere   | nce Hardv   | vare architecture                               | 23 |

|   | 2.2  | Refere   | ence softwa | are architecture                                | 24 |

|   | 2.3  | Basic a  | assumption  | ns and terminology                              | 26 |

|   | 2.4  | RT Scl   | heduling o  | n single processors                             | 26 |

|   |      | 2.4.1    | RM and      | EDF                                             | 27 |

|   |      | 2.4.2    | Priority (  | Ceiling                                         | 27 |

|   |      | 2.4.3    | Stack Re    | source Policy (SRP)                             | 28 |

|   |      | 2.4.4    | Preempti    | on Thresholds                                   | 30 |

|   | 2.5  | RT sch   | neduling or | n Multiprocessors                               | 30 |

|   |      | 2.5.1    | Classific   | ations                                          | 31 |

|   |      | 2.5.2    | Why Rea     | al-Time Multiprocessor scheduling is difficult? | 32 |

|   |      | 2.5.3    | Bin-Pack    | ting Algorithms                                 | 34 |

|   |      | 2.5.4    | Resource    | e sharing protocols                             | 34 |

|   |      |          | 2.5.4.1     | Classical blocking approaches                   | 35 |

|   |      |          | 2.5.4.2     | Wait Free approaches                            | 35 |

|   |      |          | 2.5.4.3     | Spin-lock and mixed approaches.                 | 35 |

|   |      | 2.5.5    | Task Mig    | gration                                         | 36 |

| 3 | Sing | gle proc | essor arch  | itectures                                       | 37 |

|   | 3.1  | Integra  | ating Preer | nption Threshold with the SRP                   | 37 |

|   | 3.2  | Optim    | izing stack | usage in Uniprocessors                          | 41 |

|   | 3.3  | Experi   | imental eva | aluation                                        | 47 |

| 4 | Hon  | nogeneo  | ous multip  | rocessors architectures                         | 51 |

|   | 4.1  | Backg    | round       |                                                 | 52 |

|   |      | 4.1.1    | Basic ass   | sumption and terminology                        | 52 |

|   |      | 4.1.2    | The MPC     | CP Multiprocessor Priority Ceiling Protocol     | 52 |

#### CONTENTS

| 4.2.2       Schedulability analysis of the MSRP       56         4.3       Optimizing stack usage in Multiprocessors       60         4.4       Comparing MSRP and MPCP       63         4.4.1       Comparing the blocking factors of MSRP and MPCP       64         4.4.2       Comparing the implementation of MSRP and MPCP       64         4.5       Experimental evaluation       65         4.5.1       Multiprocessor experiments       65         4.5.2       MPCP vs. MSRP comparison on generic task sets       66         4.5.3       MPCP vs. MSRP comparison on a power-train case       69         4.5.3.1       The Power-train Control Application       69         4.5.3.2       Experimental setup       72         4.5.3.3       Results       73                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 4.2  | Sharin | g Resources in Multiprocessors                  | 54 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|--------|-------------------------------------------------|----|

| 4.3Optimizing stack usage in Multiprocessors604.4Comparing MSRP and MPCP634.4.1Comparing the blocking factors of MSRP and MPCP644.4.2Comparing the implementation of MSRP and MPCP644.5Experimental evaluation654.5.1Multiprocessor experiments654.5.2MPCP vs. MSRP comparison on generic task sets664.5.3MPCP vs. MSRP comparison on a power-train case694.5.3.1The Power-train Control Application694.5.3.2Experimental setup724.5.3.3Results734.5.4Final comments755Heterogeneous multiprocessors architectures775.1System Model795.3Problem definition795.4DSP scheduling under fixed priorities835.4.2Allowing interleaving DSP requests865.5DSP scheduling under dynamic priorities905.5.1EDF with Checkpoints925.5.2Resources and checkpoints945.5.4Using CEDF+SRP for DSP scheduling985.5.4.1Collecting Bandwidth985.5.4.2Using collected bandwidth for DSP scheduling101                                                                                                                                                                                                                                                                                                                                  |   |      | 4.2.1  | Multiprocessor Stack Resource Policy (MSRP)     | 54 |

| 4.4       Comparing MSRP and MPCP       63         4.4.1       Comparing the blocking factors of MSRP and MPCP       64         4.4.2       Comparing the implementation of MSRP and MPCP       64         4.5       Experimental evaluation       65         4.5.1       Multiprocessor experiments       65         4.5.2       MPCP vs. MSRP comparison on generic task sets       66         4.5.3       MPCP vs. MSRP comparison on a power-train case       69         4.5.3.1       The Power-train Control Application       69         4.5.3.2       Experimental setup       72         4.5.3.3       Results       73         4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and check |   |      | 4.2.2  | Schedulability analysis of the MSRP             | 56 |

| 4.4.1Comparing the blocking factors of MSRP and MPCP644.4.2Comparing the implementation of MSRP and MPCP644.5Experimental evaluation654.5.1Multiprocessor experiments654.5.2MPCP vs. MSRP comparison on generic task sets664.5.3MPCP vs. MSRP comparison on a power-train case694.5.3.1The Power-train Control Application694.5.3.2Experimental setup724.5.3.3Results734.5.4Final comments755Heterogeneous multiprocessors architectures775.1System Model775.2Task Model795.3Problem definition795.4DSP scheduling under fixed priorities835.4.2Allowing interleaving DSP requests865.5DSP scheduling under dynamic priorities905.5.1EDF with Checkpoints925.5.2Resources and checkpoints945.5.4Using CEDF+SRP for DSP scheduling985.5.4.1Collecting Bandwidth985.5.4.2Using collected bandwidth for DSP scheduling101                                                                                                                                                                                                                                                                                                                                                                                             |   | 4.3  | Optimi | izing stack usage in Multiprocessors            | 60 |

| 4.4.2       Comparing the implementation of MSRP and MPCP       64         4.5       Experimental evaluation       65         4.5.1       Multiprocessor experiments       65         4.5.2       MPCP vs. MSRP comparison on generic task sets       66         4.5.3       MPCP vs. MSRP comparison on a power-train case       69         4.5.3.1       The Power-train Control Application       69         4.5.3.2       Experimental setup       72         4.5.3.3       Results       73         4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling           |   | 4.4  | Compa  | aring MSRP and MPCP                             | 63 |

| 4.5       Experimental evaluation       65         4.5.1       Multiprocessor experiments       65         4.5.2       MPCP vs. MSRP comparison on generic task sets       66         4.5.3       MPCP vs. MSRP comparison on a power-train case       69         4.5.3.1       The Power-train Control Application       69         4.5.3.2       Experimental setup       72         4.5.3.3       Results       73         4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4.1       Collecting Bandwidth       98         5.5                                    |   |      | 4.4.1  | Comparing the blocking factors of MSRP and MPCP | 64 |

| 4.5.1       Multiprocessor experiments       65         4.5.2       MPCP vs. MSRP comparison on generic task sets       66         4.5.3       MPCP vs. MSRP comparison on a power-train case       69         4.5.3.1       The Power-train Control Application       69         4.5.3.2       Experimental setup       72         4.5.3.3       Results       73         4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.2       Using collected bandwidth for DSP scheduling       98                                                                               |   |      | 4.4.2  | Comparing the implementation of MSRP and MPCP   | 64 |

| 4.5.2       MPCP vs. MSRP comparison on generic task sets       66         4.5.3       MPCP vs. MSRP comparison on a power-train case       69         4.5.3.1       The Power-train Control Application       69         4.5.3.2       Experimental setup       72         4.5.3.3       Results       73         4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                           |   | 4.5  | Experi | mental evaluation                               | 65 |

| 4.5.3       MPCP vs. MSRP comparison on a power-train case       69         4.5.3.1       The Power-train Control Application       69         4.5.3.2       Experimental setup       72         4.5.3.3       Results       73         4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       83         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                          |   |      | 4.5.1  | Multiprocessor experiments                      | 65 |

| 4.5.3.1       The Power-train Control Application       69         4.5.3.2       Experimental setup       72         4.5.3.3       Results       73         4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5.1       EDF with Checkpoints       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                       |   |      | 4.5.2  | MPCP vs. MSRP comparison on generic task sets   | 66 |

| 4.5.3.2       Experimental setup       72         4.5.3.3       Results       73         4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                            |   |      | 4.5.3  | MPCP vs. MSRP comparison on a power-train case  | 69 |

| 4.5.3.3       Results       73         4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                           |   |      |        | 4.5.3.1 The Power-train Control Application     | 69 |

| 4.5.4       Final comments       75         5       Heterogeneous multiprocessors architectures       77         5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       98                                                                                                                                                                                                                                                                                   |   |      |        | 4.5.3.2 Experimental setup                      | 72 |

| 5       Heterogeneous multiprocessors architectures       77         5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                              |   |      |        | 4.5.3.3 Results                                 | 73 |

| 5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                   |   |      | 4.5.4  | Final comments                                  | 75 |

| 5.1       System Model       77         5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                   | 5 | Heta | rogene | ous multiprocessors architectures               | 77 |

| 5.2       Task Model       79         5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 |      |        | -                                               |    |

| 5.3       Problem definition       79         5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | •      |                                                 |    |

| 5.4       DSP scheduling under fixed priorities       82         5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |        |                                                 |    |

| 5.4.1       Enhancing schedulability under fixed priorities       83         5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      |        |                                                 |    |

| 5.4.2       Allowing interleaving DSP requests       86         5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | Э.т  |        | • •                                             |    |

| 5.4.3       Simulation results       86         5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      |        |                                                 |    |

| 5.5       DSP scheduling under dynamic priorities       90         5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      |        |                                                 |    |

| 5.5.1       EDF with Checkpoints       92         5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 55   |        |                                                 |    |

| 5.5.2       Resources and checkpoints       94         5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 5.5  |        |                                                 |    |

| 5.5.3       Implementation issues       98         5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      |        | -                                               |    |

| 5.5.4       Using CEDF+SRP for DSP scheduling       98         5.5.4.1       Collecting Bandwidth       98         5.5.4.2       Using collected bandwidth for DSP scheduling       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |        |                                                 |    |

| 5.5.4.1Collecting Bandwidth985.5.4.2Using collected bandwidth for DSP scheduling101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      |        | -                                               |    |

| 5.5.4.2 Using collected bandwidth for DSP scheduling 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      | 5.5.4  |                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |        | -                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |        |                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 555    |                                                 |    |

6 Conclusions

109

# **List of Figures**

| 1.1 | The Janus Dual Processor system.                                                                                                                    | 20 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

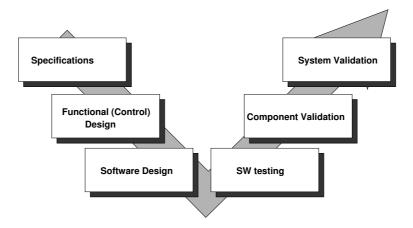

| 2.1 | V-shaped methodology.                                                                                                                               | 25 |

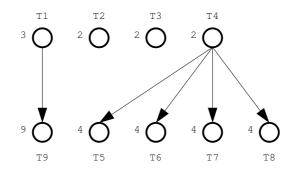

| 2.2 | The task set is composed by nine tasks with precedence constraints and a priority proportional to their sequence number. The execution time of each |    |

|     | task is shown near the balls.                                                                                                                       | 32 |

| 2.3 | The optimal schedule (finishing time = 12).                                                                                                         | 33 |

| 2.4 | The schedule obtained changing task priorities (the order now is T1, T2,                                                                            |    |

|     | T4, T5, T6, T3, T9, T7, T8) (finishing time = 14). $\dots \dots \dots \dots \dots$                                                                  | 33 |

| 2.5 | The schedule obtained adding a new processor (finishing time = 15). $\ldots$                                                                        | 33 |

| 2.6 | The schedule obtained reducing the execution times by 1 (finishing time =                                                                           |    |

|     | 13)                                                                                                                                                 | 33 |

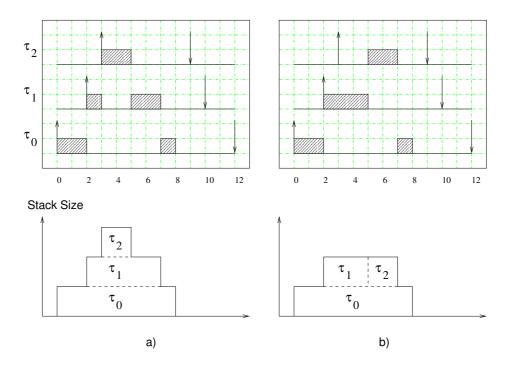

| 3.1 | Two different schedules for the same task set: <b>a</b> ) full-preemptive schedule;                                                                 |    |

|     | <b>b</b> ) preemption is disabled between $\tau_1$ and $\tau_2$ .                                                                                   | 38 |

| 3.2 | An example: The minimum total stack size does not corresponds to the                                                                                |    |

|     | minimum number of non-preemptive groups: a) Initial task set b) com-                                                                                |    |

|     | putation of the preemption thresholds c) reordering d) computation of the                                                                           |    |

|     | maximal groups)                                                                                                                                     | 42 |

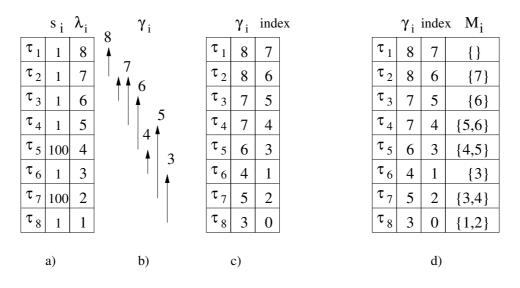

| 3.3 | Algorithm for finding the maximal groups                                                                                                            | 43 |

| 3.4 | The create_group() recursive function.                                                                                                              | 45 |

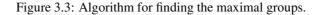

| 3.5 | Mean number of explored solutions for different task set sizes                                                                                      | 47 |

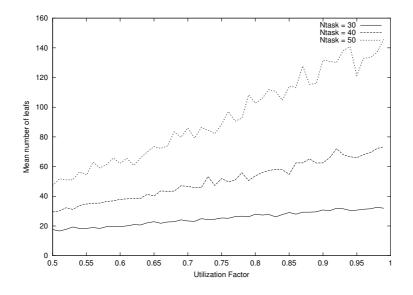

| 3.6 | Mean number of <i>cuts</i> for different task set sizes                                                                                             | 48 |

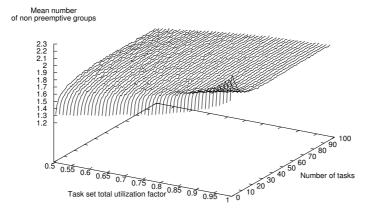

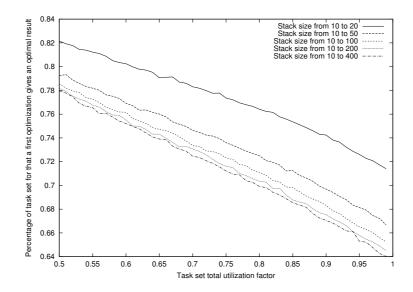

| 3.7 | Average number of preemption groups.                                                                                                                | 49 |

| 3.8 | Average number of preemption groups for different task set sizes                                                                                    | 49 |

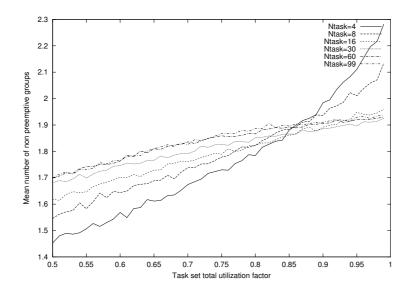

| 3.9 | Ratio of improvement given by my optimization algorithm                                                                                             | 50 |

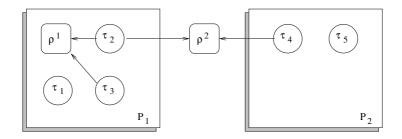

| 4.1 | Structure of the example.                                                                                                                           | 56 |

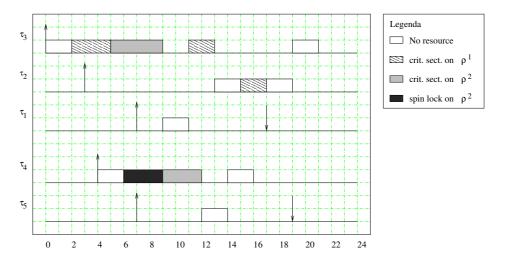

| 4.2 | An example of schedule produce by the MSRP on two processors                                                                                        | 57 |

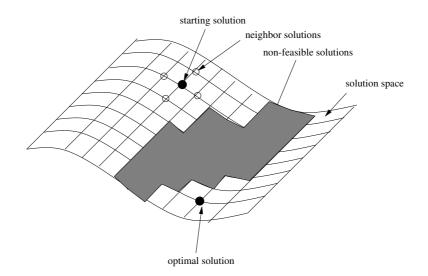

| 4.3 | Non feasible solutions must be accepted in order to reach the optimal solution.                                                                     | 62 |

| 4.4 | Simulated Annealing Algorithm.                                                                                                                      | 63 |

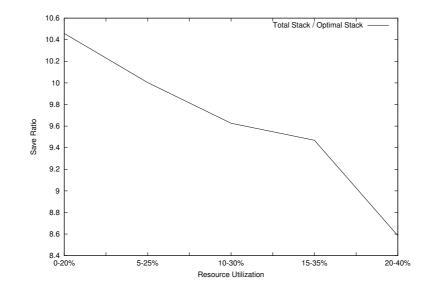

| 4.5 | Ratio of improvement given by my multiprocessor optimization algorithm                                                                              |    |

|     | when varying the utilization of shared resources                                                                                                    | 66 |

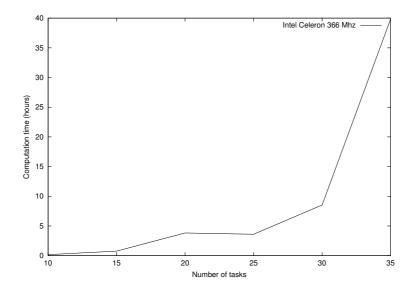

| 4.6  | Average computation times for the simulated annealing algorithm as a func-                   |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | tion of the problem size.                                                                    | 67 |

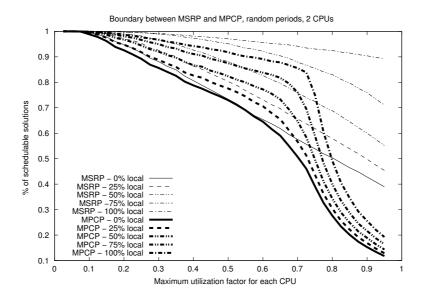

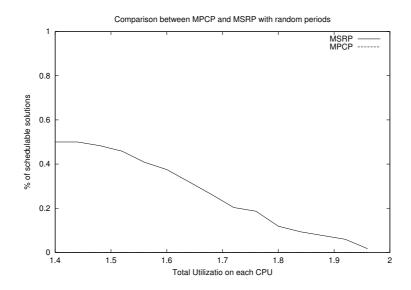

| 4.7  | Percentage of schedulable solutions, random periods, variable percentage                     |    |

|      | of local resource utilization.                                                               | 68 |

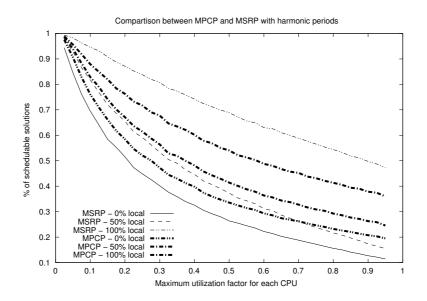

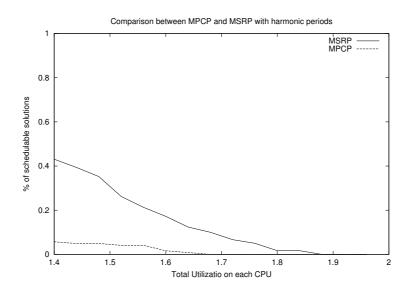

| 4.8  | Percentage of schedulable solutions, harmonic periods, variable percentage                   |    |

|      | of local resource utilization.                                                               | 68 |

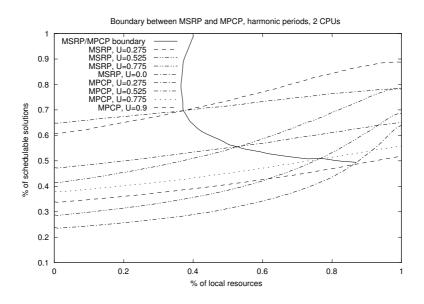

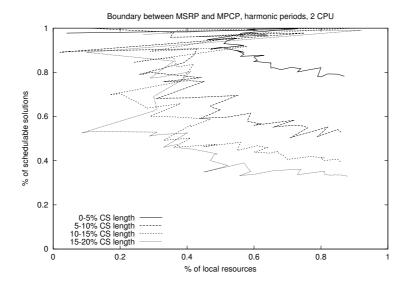

| 4.9  | Comparison of MPCP and MSRP with the performance boundary (Y=percenta                        | ge |

|      | of schedulable solutions, X=percentage of local critical sections)                           | 69 |

| 4.10 | Boundary obtained considering 2 CPUs with various resource usages                            | 70 |

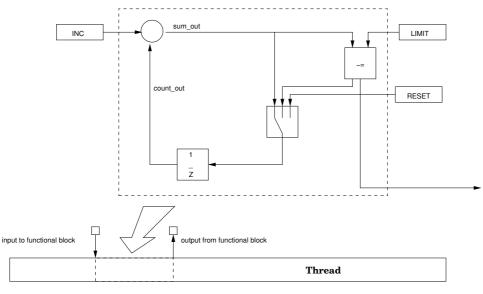

| 4.11 | A thread contains the implementation of several functional blocks $\ldots$ .                 | 71 |

| 4.12 | Percentage of schedulable task sets with randomly selected periods on Janus                  |    |

|      | by MPCP/MSRP.                                                                                | 74 |

| 4.13 | Percentage of schedulable task sets with harmonic periods on Janus by                        |    |

|      | MPCP/MSRP                                                                                    | 74 |

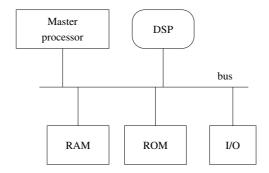

| 5.1  | Block diagram of the system architecture.                                                    | 79 |

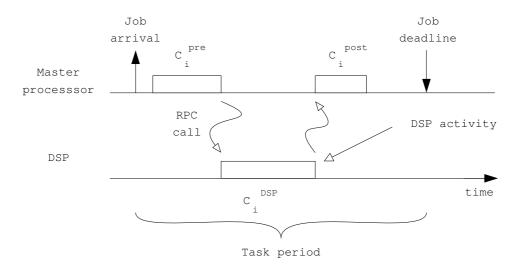

| 5.2  | Structure of a DSP task.                                                                     | 80 |

| 5.3  | A task set that cannot be feasibly scheduled by RM and EDF (jobs of task                     |    |

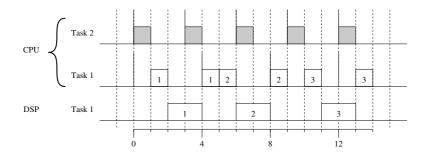

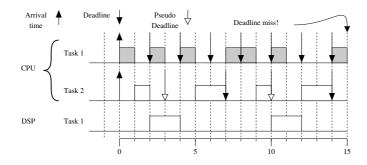

|      | $\tau_1$ are numbered to facilitate interpretation): task $\tau_1$ misses all its deadlines. | 80 |

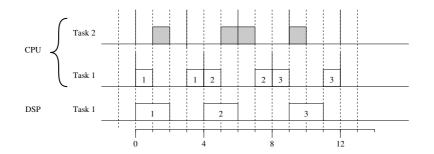

| 5.4  | A feasible schedule achieved by a different priority assignment $(P_1 > P_2)$ .              | 81 |

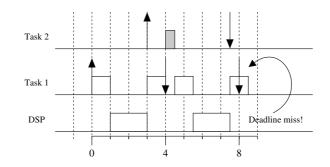

| 5.5  | EDF does not work always.                                                                    | 82 |

| 5.6  | Also EDF with modified deadlines does not work always                                        | 82 |

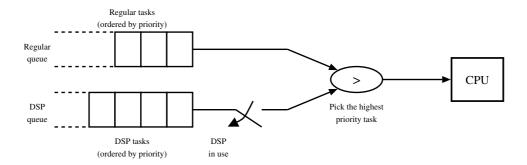

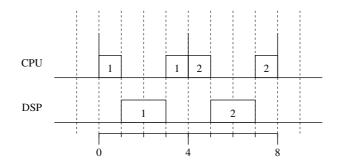

| 5.7  | My scheduling approach. When the DSP is active, the scheduler selects                        |    |

|      | tasks from the regular queue only.                                                           | 83 |

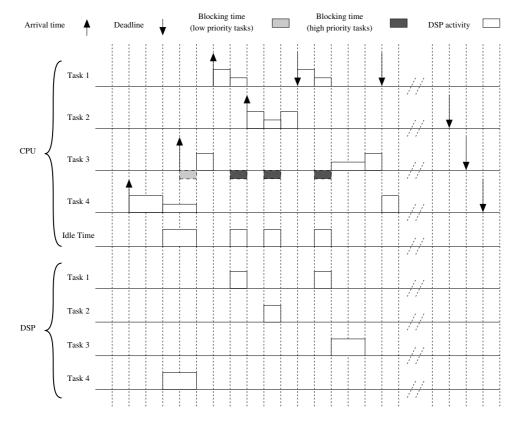

| 5.8  | Example of scenario where task $\tau_3$ is blocked by some high priority ( $\tau_1$ and      |    |

|      | $\tau_2$ ) and low priority ( $\tau_4$ ) tasks.                                              | 85 |

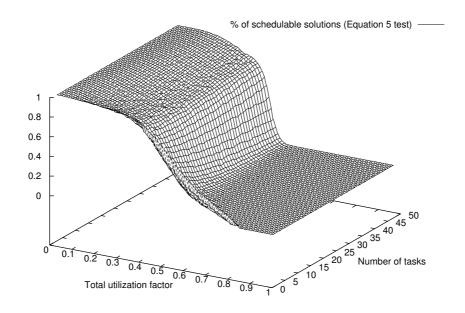

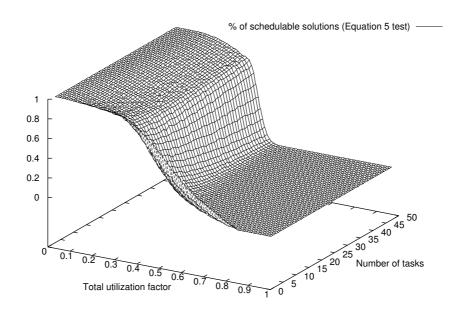

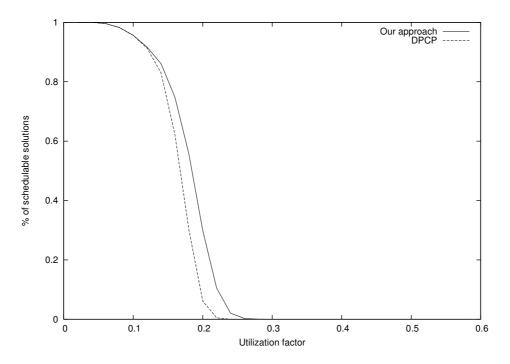

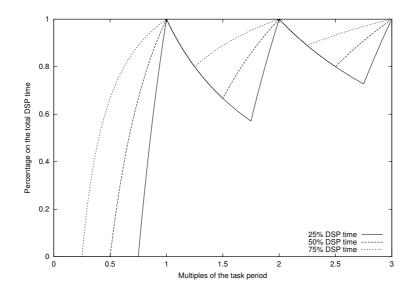

| 5.9  | Schedulability results of my approach when varying the total utilization                     |    |

|      | factor and the number of tasks in the task set (using Equation (5.3) )                       | 87 |

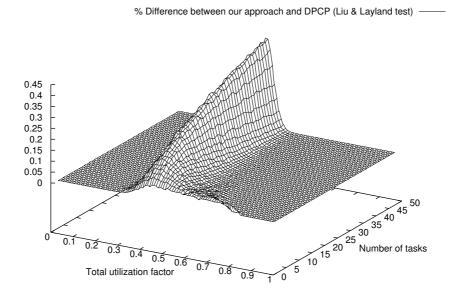

| 5.10 | Schedulability results of DPCP when varying the total utilization factor and                 |    |

|      | the number of tasks in the task set (using Equation (5.3))                                   | 88 |

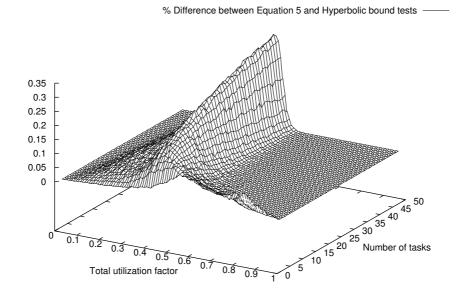

| 5.11 | Difference between the two approaches (using Equation (5.3))                                 | 88 |

| 5.12 | Improvement achieved using the Hyperbolic Bound                                              | 89 |

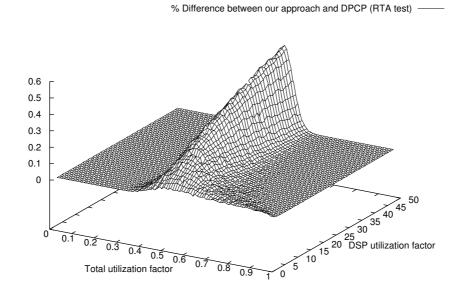

| 5.13 | Difference between the two approaches (using response time analysis)                         | 89 |

| 5.14 | Performance of the two approaches and their difference as a function of the                  |    |

|      | utilization factor for task sets composed by 30 tasks                                        | 90 |

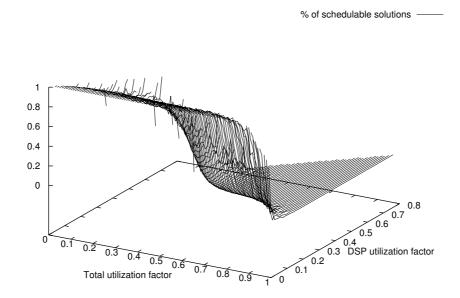

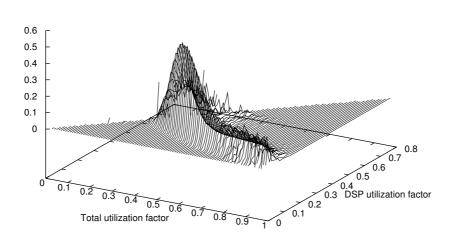

| 5.15 | Difference in the percentage of scheduled tasks set between my approach                      |    |

|      | and DPCP when considering the influence of DSP utilization                                   | 91 |

| 5.16 | Influence of DSP utilization on the schedulability                                           | 91 |

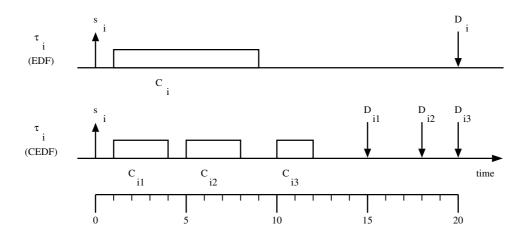

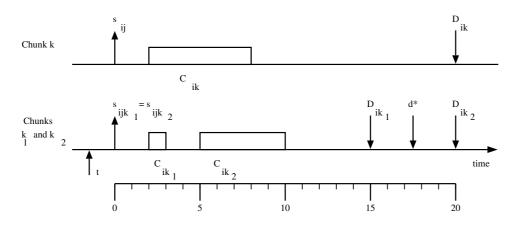

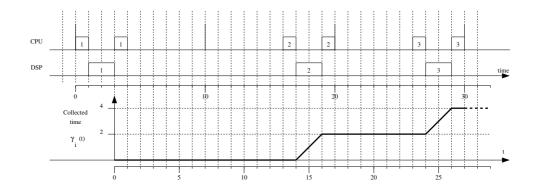

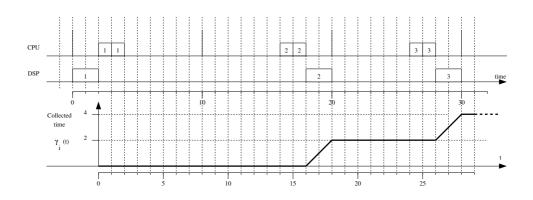

| 5.17 | A task scheduled by EDF and CEDF. The task has the following structure:                      |    |

|      | $D_i = 20, C_i = 8, m_i = 3, C_{i1} = 3, C_{i2} = 3, C_{i3} = 2.$                            | 93 |

| 5.18 | A single transformation step                                                                 | 93 |

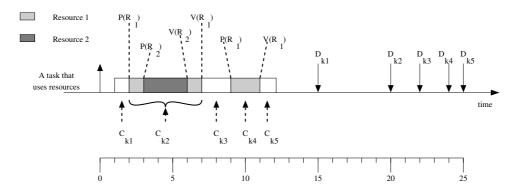

| 5.19 | A typical checkpoint assignment used in the CEDF+SRP Algorithm                               | 95 |

12

#### LIST OF FIGURES

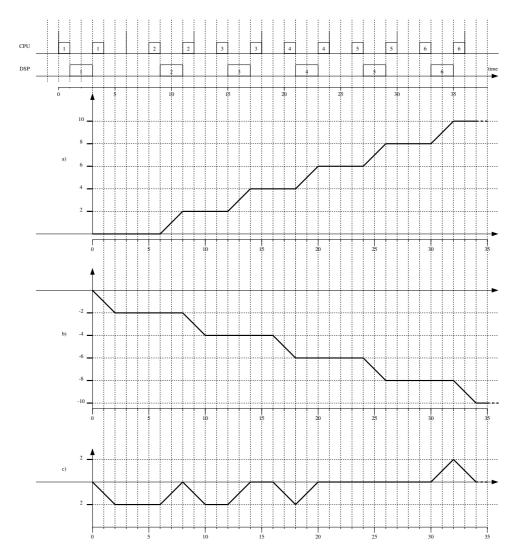

| 5.20 Task executions are not nested under CEDF+SRP. Note that task $\tau_i$ post-                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| pones its deadline at time 2; task $\tau_j$ postpones its deadline at time 6 96                                                                           |

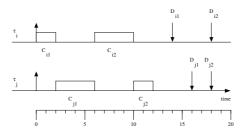

| 5.21 An example. The Figure shows only two instances (numbered with '1' and                                                                               |

| '2') of the periodic task                                                                                                                                 |

| 5.22 The lower bound on the collected time $\gamma_i(t)$ of a task $\tau_i$ with $T_i = 10$ and                                                           |

| $C_i = 4$ ; task $\tau_i$ is divided in three chunks (the second runs on a DSP) with                                                                      |

| capacities $C_{i1} = 1, C_{i2} = 2$ , and $C_{i3} = 1,,,,,,$ 100                                                                                          |

| 5.23 If the exact distribution of the DSP computation is not known, a conserva-                                                                           |

| tive approach can be applied (compare this figure with Figure 5.22) 100                                                                                   |

| 5.24 An acceptance test that consider more than one DSP task                                                                                              |

| 5.25 A function $\mu(t)$ for a task with execution time $C_i = 2$ and period $T_i = 5$ . 103                                                              |

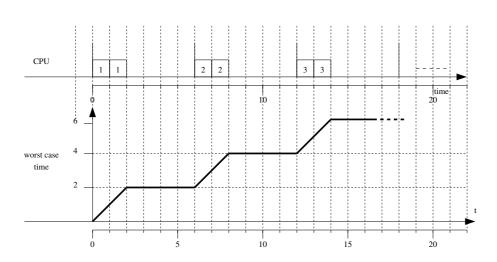

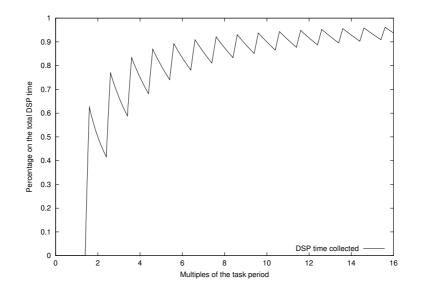

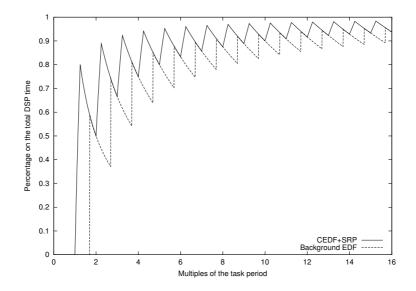

| 5.26 Percentage of DSP time collected by $\gamma_i(t)$ using the settings on Figure 5.22. 105                                                             |

| 5.27 Percentage of DSP Time collected with different task settings 106                                                                                    |

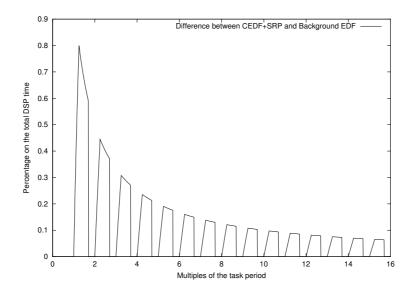

| 5.28 Comparison between the collected DSP time using CEDF+SRP and SRP                                                                                     |

| with a big relative deadline. The parameter of the DSP task were $P = 100$ ,                                                                              |

| $C_{i1} = 5, C_{i3} = 45, C_{i2} = 25. \dots \dots$ |

| 5.29 Difference between the two plots of Figure 5.28                                                                                                      |

| 5.30 An example showing the constructive method of Section <b>??</b> : a) $\Gamma(t) =$                                                                   |

| $\gamma_1(t)$ after accepting $\tau_1$ ; b) the function $-\mu_3(t)$ ; c) $\Gamma(t) = \gamma_1(1) - \mu_3(t)$                                            |

| after accepting $\tau_3$                                                                                                                                  |

### LIST OF FIGURES

# **List of Tables**

| 1.1 | Typical memory sizes for system-on-a-chip                     |

|-----|---------------------------------------------------------------|

| 2.1 | A Simple classification of parallel programming styles        |

| 4.1 | The example task set                                          |

| 5.1 | Periods and CPU utilization for tasks $\tau_4$ to $\tau_{11}$ |

### LIST OF TABLES

# **Chapter 1**

# Introduction

The Digital Revolution that is happening in the last twenty years is slowly changing the way products are designed and used. We live in a world of increasingly intrusive information technology, requiring informations to be always available in the right places, asking more and more features to the final products.

Tight requirements and new features are now common also in mechanical systems, where different objectives (ecological reasons for pollution reduction, integration of different subsystems, higher requirements for control performance) constantly adds complexity to the embedded controllers used to control the physical systems.

All these electronic systems needs to have some kind of relationship with the environment they are working in, because in some way they have to communicate informations (e.g., the temperature of a room, the weight of the people that are on a lift) or to directly control some mechanical parts (e.g., they have to set the spark timing in a car engine). This interaction is related to giving the result of the computation *in time*, that intuitively means the results have to be somehow synchronized with the response times of the external environment. For example, if you press the brake pedal of a car while driving, you would like to reduce the speed of the car *as soon as possible*; if you watch a movie using a DVD player, you probably want to *see* the movie and to ear the sound in a *synchronized* way.

All these implicit requirements are translated at design time in temporal constraints. For example, in the case of the brake pedal, the time elapsed between the press of the pedal by the the driver and the start of the brake action on the wheel should be in the order of the response time of the human brain that is driving the car, that is, probably, a few milliseconds (ms). That time sets an end-to-end requirement, that have to be met by properly choosing the mechanics and the electronics composing the braking system. In the example of the movie, once the sound of the movie started the DVD player has to display one frame every 40 ms, to give the idea to the human brain that is watching the TV set that he is seeing a movie and not a set of still frames.

All these computing environments that have to interact with the outside environment are called *real-time* systems. There are different kind of real-time systems, depending on the criticality of the synchronization that have to be reached with the environment. It is out of the scope of this thesis to make a comprehensive enumeration of real-time systems;

however, an important distinction between the so-called *hard* real-time systems (where the violation of a time requirement may be catastrophic) and other kind of systems, often called *soft* real-time-systems (where the consequence of a bad timing is just a performance degradation) is needed.

Furthermore, it is worth noting that real-time features only become a problem when the available resources are limited. For example, in a DVD player, cost and thermical reasons may force the use of less powerful computing architectures that are cheap and do not require a fan. These architectures may need an adequate resource scheduling policy to make efficient use of the (little) computing power available.

Real-time systems are often *concurrent* systems. The notion of concurrency (that means the ability of doing many things at the same time) is again linked to the lack of physical resources. For example, a microwave oven have to perform different concurrent tasks while heating up your hamburger: it has to produce the microwaves that cooks your food, rotate the dish to perform a proper uniform cooking, countdown and update the LCD with the remaining cooking time, and check if the user opens the oven's door, to eventually stop producing the microwaves.

Such a small embedded device like a microwave oven is probably controlled by a single CPU embedded behind the buttons and the LCD display of the man-machine interface. The software running on that CPU has to *schedule* properly different activities, and make them behave as they each run on a dedicated CPU.

The software that runs on the CPU is often divided in different layers. A common distinction is made between the *application* (the cooking algorithms, that are specific for each microwave oven) and the *firmware* (that is the infrastructure on which the application runs, that typically can be reused to design other embedded systems, such as coffee machines).

Most of the real-time systems academic research deals with the basic question of "what is the best way to design the firmware of a real-time system?". Many answers have been found for different kind of systems, related to different design parameters like:

- the number of entities (CPUs) available in the system;

- the kind of *scheduling algorithm* that is chosen for running the different *tasks* of the application;

- the kind of synchronization mechanisms of the different activities;

- the kind of *cooperation* required to accomplish a task (are these tasks all independent or do they need to share information?);

- the kind of *communication* between different tasks in the system (we consider only shared memory architectures or also distributed systems connected through a network?);

- the amount of resources available (can advanced features be implemented or should we save as much resources as possible to have a cheaper final product).

This thesis addresses some solutions for the design of a firmware for real time systems that takes in account the design parameters just listed.

#### 1.1. WHY MULTIPROCESSORS?

In particular, the thesis proposes some techniques for the design of the firmware of embedded system-on-a-chip (SoC) that in general are composed by more than one CPU, and that have to be designed taking in account the amount of available resources (in my case, the RAM space used for stacks).

# 1.1 Why multiprocessors?

The first question which needs an answer is why there is a real need for multiprocessor SoC. If we analyze the trend for the integration of future applications in the embedded market, and especially in the automotive market [28], it is clear that a standard uniprocessor microcontroller architecture will not be able to support the needed computing power even taking into account the IC technology advances.

To increase computational power in embedded real-time systems there are then two possible ways:

- to increase the processor speed;

- to increase the parallelism of the architecture.

The first option requires the use of caching, deep pipelining or other advanced architectures. This solution suffers from serious drawbacks in the context of real-time embedded systems: caching makes very hard or impossible to determine the worst case execution times of programs; deep pipelining is not effective because of the large number of stalls caused by reactions to asynchronous events. Also, parallelism at the instruction level (VLIW architectures) requires large silicon areas and drastically increases code size.

Therefore, the best option and the future of many embedded applications seems to rely on the adoption of multiple-processor-on-a-chip architectures.

This idea, that was a seminal idea only four years ago, now has reached some kind of maturity; in fact, many multiprocessor SoC are now available on the marketplace.

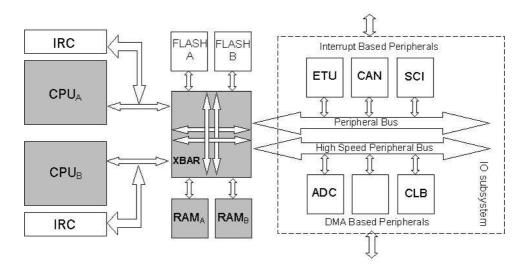

The Janus microcontroller (see the scheme of Figure 1.1), developed by PARADES, ST Microelectronics and Magneti Marelli in the context of the MADESS[45] project, is an example of a dual-processor platform for power-train applications. Two 32-bit ARM7TDMI processors connected by a crossbar switch to 4 memory banks and two peripheral buses for I/O processing (low and high bandwidth) provide twofold computational power, compared to a single (ARM7TDMI) processor architecture, at very low increment of the silicon area, i.e. at comparable system costs. Both CPUs share the same address space. The main memory is organized in different modules and types: SRAM and FLASH. In architectures with multiple processors, memory access is the most important bottleneck of the system. Almost any communication flow is between the memory and other system components. To allow a correct synchronization and communication among tasks allocated to different processors, the architecture provides hardware support for inter-processor communication by interrupt inter-processor mechanisms and for shared memory by atomic test-and-set.

Although Janus implements a symmetric multiprocessor, there are other promising symmetric architectures composed by a RISC processor (or a microcontroller) and one

Figure 1.1: The Janus Dual Processor system.

or more DSPs [55, 35]. For example, the Texas Instruments SMJ320C80 is a single-chip MIMD<sup>1</sup> parallel processor that consists of a 32-bit RISC master processor, four 32-bit parallel DSPs, a transfer controller, and a video controller. All the processors are tightly coupled through an on-chip crossbar switch that provides access to a shared on-chip RAM.

Recently, Altera Corporation released a new version of its Nios II embedded processor [22], that is a 32 bit platform designed to be mapped on FPGA devices. In that way, the user can build a system with several processors, each one doing its specific job. Just to give an idea of the level of parallelism that can be implemented with those systems, a NIOS II processor can use from 700 to 2000 logic elements (depending on its configuration), whereas Altera's FPGAs for NIOS systems range from 3 to 40K logic elements, meaning that these FPGAs may potentially have tens of processors on a single chip.

Many other designs will be also available on the market soon, bringing the possibility to really use and take advantage of the increased power provided by multiprocessor.

The applications running on these new single-chip platforms require predictable (and fast) scheduling algorithms. In addition, kernels must fit in a few kilobytes of memory, and, together with the application, they must use the smallest possible amount of RAM memory. Resource sharing must be carefully handled and all communication primitives on shared memory must be designed in order to allow only a limited blocking time.

Moreover, the main problem with these systems is that there there is not a common way of exploiting these multiprocessor architectures in an efficient and scalable way. The purpose of this thesis is to find ways to use these systems without wasting the computing power available.

<sup>&</sup>lt;sup>1</sup>Multiple Instruction Multiple Data.

| Chip name  | Description                    | ROM    | RAM   |

|------------|--------------------------------|--------|-------|

| AT91M40800 | Atmel 32 bit ARM7 SoC          | -      | 4 Kb  |

| AT91F40816 | Atmel 32 bit ARM7 Soc          | 3 Mb   | 8 Kb  |

| H8/3297    | Hitachi 8 bit microcontroller  | 60 Kb  | 2 Kb  |

| ST10F269   | Siemens 16 bit microcontroller | 256 Kb | 12 Kb |

| Janus      | Double ARM7 by ST, PARADES, MM | 256 Kb | 64 Kb |

Table 1.1: Typical memory sizes for system-on-a-chip.

### **1.2 Saving RAM space**

Many embedded applications are designed on SoC architectures to reduce the cost of the final product. In these systems, RAM is extremely expensive in terms of chip space, and it heavily impacts on the cost of the final product (it is often necessary to re-design part of the application just to save a few RAM bytes).

Table 1.1 shows the memory space on a set of microcontrollers available on the market. As it can be seen, ROM memory (typically flash memory) is ten times bigger than the available RAM. That fact is justified because each cell of RAM can be implemented using 6 transistors, whereas a cell of Flash memory can be implemented with only one, allowing higher density.

Since, in general, there is a limited memory (both ROM and RAM) on a SoC, the application and the firmware must use the smallest possible amount of RAM memory.

In the design of the kernel mechanisms for such small embedded systems, it has been clear from the beginning that the choice of the real-time scheduling discipline influences both the memory utilization and the system overhead. For example, selecting a non preemptive scheduling algorithm can greatly reduce the overall requirement of stack memory whereas using a preemptive algorithm could increase the processor utilization.

For this reason, it has been very important to exploit different combinations and configurations of scheduling algorithms and services and to develop new ones in order to find the best kernel mechanisms for minimizing the memory requirements without jeopardizing the timing constraints.

To reduced the RAM space, proper design techniques (like the preemption threshold techniques) have been successfully developed in the past years, allowing a significant reduction of the stack usage in the entire system.

This thesis addresses the problems of memory optimization for multiprocessors SoC, extending the existing techniques for stack minimization to multiprocessors and to dynamic scheduled systems.

# **1.3 Thesis contributions**

The main contributions of this thesis to the state of the art in design of the firmware for mono and multiprocessor system-on-a-chip is that I developed a complete methodology for minimizing the memory utilization of real-time task sets, communicating through shared memory, in uniprocessor and multiprocessor systems. Moreover, I developed new techniques for scheduling in heterogeneous multiprocessors.

The contributions are detailed in the following points (points 1 to 4 are related to mono processor architectures, the rest for multiprocessor architectures):

- 1. I designed a novel scheduling algorithm, called **SRPT**, that allows the use of one single stack for all the real-time tasks under dynamic priority scheduling (Earliest Deadline) schemes.

- 2. I designed an optimization procedure for assigning the scheduling parameters (preemption thresholds and grouping of tasks in non-preemptive sets) so that the maximum stack size is minimized without jeopardizing the schedulability of the task set.

- 3. I designed a novel scheduling algorithm called **MSRP**, that allows real-time tasks, allocated on different processor, to communicate/interact through shared memory; each task is statically allocated to one processor, and all tasks on one processor share the same stack.

- I designed and implemented an optimization procedure for assigning tasks to processors and for assigning the scheduling parameters, so to minimize the overall stack size.

- 5. I designed a new scheduling algorithm for scheduling heterogeneous multiprocessor systems using fixed priorities.

- 6. I designed a new scheduling algorithm for scheduling heterogeneous multiprocessor systems using EDF scheduling.

### **1.4** Thesis outline

The remainder of this thesis is structured as follows.

Chapter 2 presents some of the techniques used as a basis for the results described in this thesis. Chapter 3 details the results found in single processor scheduling, such as the SRPT algorithm, and the stack minimization procedures. Chapter 4 describes the results obtained for homogeneous multiprocessors, must notably the MSRP scheduling algorithm, its comparison with the MPCP algorithm, and the allocation procedure that assigns tasks to processors. Chapter 5 describes the results on heterogeneous multiprocessors, and finally Chapter 6 gives the implications of the results in this thesis, and some possible future works on these topics.

# **Chapter 2**

# Background

The purpose of this chapter is to give a background knowledge that will help the reader understanding the rest of the thesis.

# 2.1 Reference Hardware architecture

Chapter 3 to Chapter 5 propose different scheduling algorithms developed on top of various abstract hardware architectures.

In general, for the purpose of this thesis I am not interested on hardware details of a specific architecture, but only to an abstract description of the hardware in terms of the following main blocks:

- **CPU.** The CPU is typically a microcontroller or a general purpose processing unit. In the case of multiprocessor architectures, an instance of the architecture may have one or more CPUs.