Indian Institute of Technology Jodhpur, Year 2018-2019

# Digital Logic and Design

(Course Code: EE222)

Lecture 20-21: Counters contd....

### Course Instructor: Shree Prakash Tiwari

Email: <a href="mailto:sptiwari@iitj.ac.in">sptiwari@iitj.ac.in</a>

Webpage: <a href="http://home.iitj.ac.in/~sptiwari/">http://home.iitj.ac.in/~sptiwari/</a> Course related documents will be uploaded on <a href="http://home.iitj.ac.in/~sptiwari/DLD/">http://home.iitj.ac.in/~sptiwari/DLD/</a>

**Note:** The information provided in the slides are taken form text books Digital Electronics (including Mano & Ciletti), and various other resources from internet, for **teaching/academic use only**

**Counters Overview**

#### ° Counters are important components in computers

- The increment or decrement by one in response to input

- ° Two main types of counters

- · Ripple (asynchronous) counters

- · Synchronous counters

- ° Ripple counters

- · Flip flop output serves as a source for triggering other flip flops

- ° Synchronous counters

- All flip flops triggered by a clock signal

- Synchronous counters are more widely used in industry.

#### **Counters**

- Asynchronous counters: the flip-flops do not change states at exactly the same time as they do not have a common clock pulse.

- Known as ripple counters, as the input clock pulse "ripples" through the counter – cumulative delay is a drawback.

- n flip-flops → a MOD (modulus) 2<sup>n</sup> counter. (Note: A MOD-x counter cycles through x states.)

- Output of the last flip-flop (MSB) divides the input clock frequency by the MOD number of the counter, hence a counter is also a frequency divider.

#### **Counters**

- ° Counter: A register that goes through a prescribed series of states

- ° Binary counter

- · Counter that follows a binary sequence

- N bit binary counter counts in binary from n to 2<sup>n-1</sup>

- ° Ripple counters triggered by initial Count signal

- ° Applications:

- Watches

- · Clocks

- · Alarms

- · Web browser refresh

#### **Asynchronous Counters**

- Each FF output drives the CLK input of the next FF.

- FFs do not change states in exact synchronism with the applied clock pulses.

- There is delay between the responses of successive FFs.

- Ripple counter due to the way the FFs respond one after another in a kind of rippling effect.

| $\mathbf{A_3}$ | $\mathbf{A}_2$ | $\mathbf{A_1}$ | $\mathbf{A}_{0}$ |

|----------------|----------------|----------------|------------------|

| 0              | 0              | 0              | 0                |

| 0              | 0              | 0              | 1                |

| 0              | 0              | 1              | 0                |

| 0              | 0              | 1              | 1                |

| 0              | 1              | 0              | 0                |

| 0              | 1              | 0              | 1                |

| 1              | 0              | 0              | 0                |

| 1              | 0              | 0              | 1                |

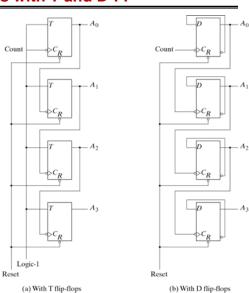

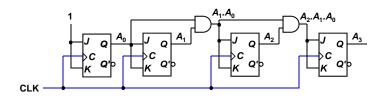

### **Binary Ripple Counters with T and D-FF**

- Reset signal sets all outputs to 0

- Count signal toggles output of low-order flip flop

- Low-order flip flop provides trigger for adjacent flip flop

- Not all flops change value simultaneously

- · Lower-order flops change first

- ° Focus on D flip flop implementation

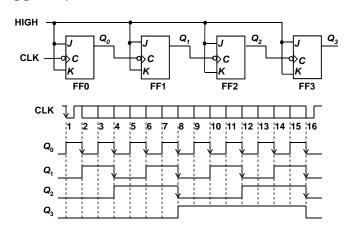

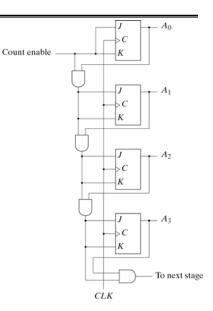

Fig. 6-8 4-Bit Binary Ripple Counter

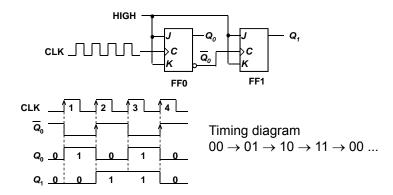

### **Asynchronous Counters**

- Example: 2-bit ripple binary counter.

- Output of one flip-flop is connected to the clock input of the next more-significant flip-flop.

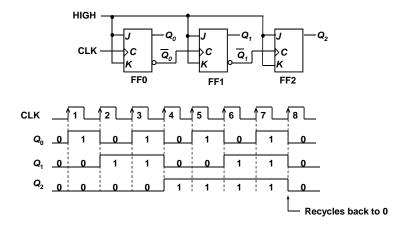

#### **Asynchronous Counters**

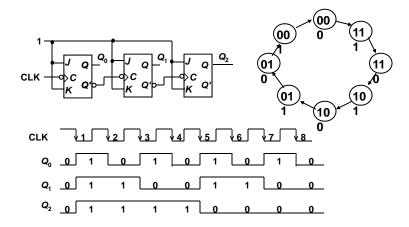

■ Example: 3-bit ripple binary counter.

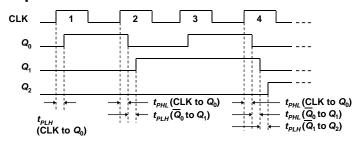

### **Asynchronous Counters**

- Propagation delays in an asynchronous (rippleclocked) binary counter.

- If the accumulated delay is greater than the clock pulse, some counter states may be misrepresented!

### **Asynchronous Counters**

Example: 4-bit ripple binary counter (negative-edge triggered).

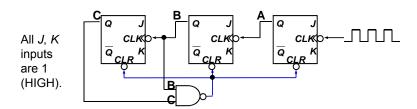

### Asynchronous Counters with MOD no. < 2<sup>n</sup>

- States may be skipped resulting in a truncated sequence.

- Technique: force counter to recycle before going through all of the states in the binary sequence.

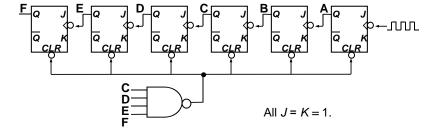

- Example: Given the following circuit, determine the counting sequence (and hence the modulus no.)

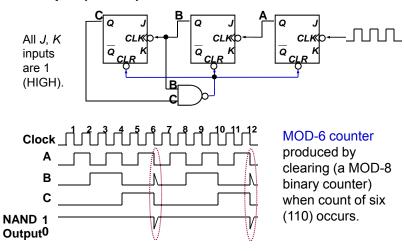

## Asynchronous Counters with MOD no. < 2<sup>n</sup>

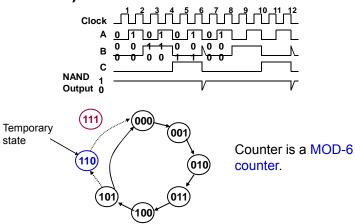

■ Example (cont'd):

### Asynchronous Counters with MOD no. < 2<sup>n</sup>

Example (cont'd): Counting sequence of circuit (in CBA order).

### Asynchronous Counters with MOD no. < 2<sup>n</sup>

- Exercise: How to construct an asynchronous MOD-5 counter? MOD-7 counter? MOD-12 counter?

- Question: The following is a MOD-? counter?

### Asynchronous Counters with MOD no. < 2<sup>n</sup>

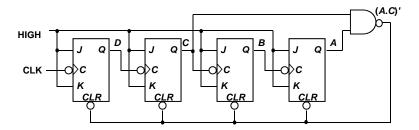

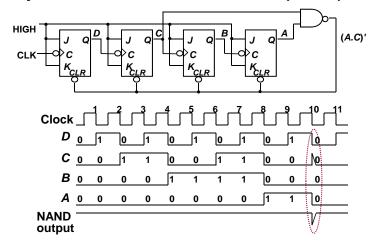

- Decade counters (or BCD counters) are counters with 10 states (modulus-10) in their sequence. They are commonly used in daily life (e.g.: utility meters, odometers, etc.).

- Design an asynchronous decade counter.

### Asynchronous Counters with MOD no. < 2<sup>n</sup>

Asynchronous decade/BCD counter (cont'd).

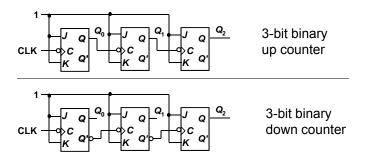

### **Asynchronous Down Counters**

- So far we are dealing with *up counters*. *Down counters*, on the other hand, count downward from a maximum value to zero, and repeat.

- Example: A 3-bit binary (MOD-2³) down counter.

### **Asynchronous Down Counters**

■ Example: A 3-bit binary (MOD-8) down counter.

#### **Cascading Asynchronous Counters**

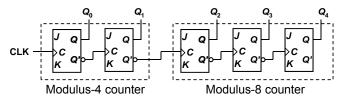

- Larger asynchronous (ripple) counter can be constructed by cascading smaller ripple counters.

- Connect last-stage output of one counter to the clock input of next counter so as to achieve higher-modulus operation.

- Example: A modulus-32 ripple counter constructed from a modulus-4 counter and a modulus-8 counter.

#### **Cascading Asynchronous Counters**

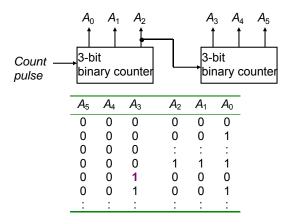

■ Example: A 6-bit binary counter (counts from 0 to 63) constructed from two 3-bit counters.

#### **Cascading Asynchronous Counters**

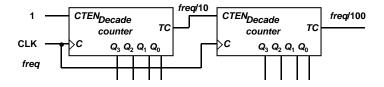

- If counter is a not a binary counter, requires additional output.

- Example: A modulus-100 counter using two decade counters.

TC = 1 when counter recycles to 0000

### **Synchronous counters**

- Synchronous(parallel) counters

- All of the FFs are triggered simultaneously by the clock input pulses.

- · All FFs change at same time

- ° Remember

- If J=K=0, flop maintains value

- If J=K=1, flop toggles

- Most counters are synchronous in computer systems.

- Can also be made from D flops

- Value increments on positive edge

Fig. 6-12 4-Bit Synchronous Binary Counter

#### Synchronous (parallel) counters

- Synchronous (parallel) counters: the flip-flops are clocked at the same time by a common clock pulse.

- We can design these counters using the sequential logic design process (will be covered in coming Lectures).

- Example: 2-bit synchronous binary counter (using T flip-flops, or JK flip-flops with identical J,K inputs).

| Present state         |       |                 | Next<br>state |                 | Flip-flop<br>inputs |  |  |

|-----------------------|-------|-----------------|---------------|-----------------|---------------------|--|--|

| <b>A</b> <sub>1</sub> | $A_0$ | $A_1^{\dagger}$ | $A_0^+$       | TA <sub>1</sub> | TA <sub>0</sub>     |  |  |

| 0                     | 0     | 0               | 1             | 0               | 1                   |  |  |

| 0                     | 1     | 1               | 0             | 1               | 1                   |  |  |

| 1                     | 0     | 1               | 1             | 0               | 1                   |  |  |

| 1                     | 1     | 0               | 0             | 1               | 1                   |  |  |

### **Synchronous (Parallel) Counters**

Example: 2-bit synchronous binary counter (using T flip-flops, or JK flip-flops with identical J,K inputs).

|                       | sent<br>ate |                 | Next<br>state |                        | -flop<br>outs |                         |

|-----------------------|-------------|-----------------|---------------|------------------------|---------------|-------------------------|

| <b>A</b> <sub>1</sub> | $A_0$       | $A_1^{\dagger}$ | $A_0^+$       | <i>TA</i> <sub>1</sub> | $TA_0$        | $TA_1 = A_0$            |

| 0                     | 0           | 0               | 1             | 0                      | 1             | $TA_1 = A_0$ $TA_0 = 1$ |

| 0                     | 1           | 1               | 0             | 1                      | 1             |                         |

| 1                     | 0           | 1               | 1             | 0                      | 1             |                         |

| 1                     | 1           | 0               | 0             | 1                      | 1             |                         |

|                       |             |                 |               | 1                      |               |                         |

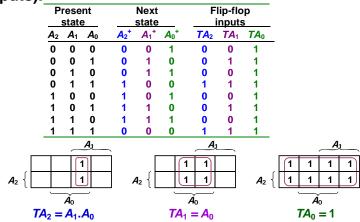

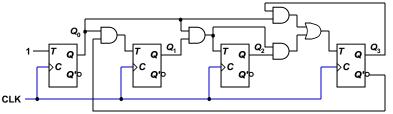

### **Synchronous (Parallel) Counters**

■ Example: 3-bit synchronous binary counter (using T flip-flops, or JK flip-flops with identical J, K inputs).\_\_\_

## **Synchronous (Parallel) Counters**

■ Example: 3-bit synchronous binary counter (cont'd).

$$TA_2 = A_1.A_0$$

$$TA_1 = A_0 TA_0 = 1$$

### **Synchronous (Parallel) Counters**

Note that in a binary counter, the n<sup>th</sup> bit (shown underlined) is always complemented whenever

or

$$\underline{0}11...11 \rightarrow \underline{1}00...00$$

or  $\underline{1}11...11 \rightarrow \underline{0}00...00$

- Hence, X<sub>n</sub> is complemented whenever X<sub>n-1</sub>X<sub>n-2</sub> ... X<sub>1</sub>X<sub>0</sub> = 11...11.

- As a result, if T flip-flops are used, then  $TX_n = X_{n-1} \cdot X_{n-2} \cdot \dots \cdot X_1 \cdot X_0$

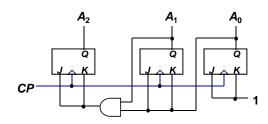

## **Synchronous (Parallel) Counters**

■ Example: 4-bit synchronous binary counter.

$$TA_3 = A_2 . A_1 . A_0$$

$TA_2 = A_1 . A_0$

$TA_1 = A_0$

$TA_0 = 1$

### **Synchronous (Parallel) Counters**

■ Example: Synchronous decade/BCD counter.

| Clock pulse  | $Q_3$ | $Q_2$ | Q <sub>1</sub> | $Q_0$ |

|--------------|-------|-------|----------------|-------|

| Initially    | 0     | 0     | 0              | 0     |

| 1            | 0     | 0     | 0              | 1     |

| 2            | 0     | 0     | 1              | 0     |

| 3            | 0     | 0     | 1              | 1     |

| 4            | 0     | 1     | 0              | 0     |

| 5            | 0     | 1     | 0              | 1     |

| 6            | 0     | 1     | 1              | 0     |

| 7            | 0     | 1     | 1              | 1     |

| 8            | 1     | 0     | 0              | 0     |

| 9            | 1     | 0     | 0              | 1     |

| 10 (recycle) | 0     | 0     | 0              | 0     |

$$\begin{split} T_0 &= 1 \\ T_1 &= Q_3'.Q_0 \\ T_2 &= Q_1.Q_0 \\ T_3 &= Q_2.Q_1.Q_0 + Q_3.Q_0 \end{split}$$

## **Synchronous (Parallel) Counters**

■ Example: Synchronous decade/BCD counter (cont'd).

$$\begin{split} T_0 &= 1 \\ T_1 &= Q_3'.Q_0 \\ T_2 &= Q_1.Q_0 \\ T_3 &= Q_2.Q_1.Q_0 + Q_3.Q_0 \end{split}$$

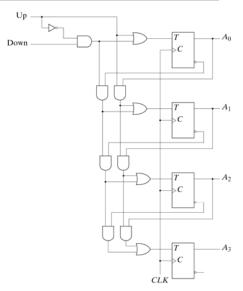

#### Synchronous UP/Down counters

- Up/Down Counter can either count up or down on each clock cycle

- Op counter counts from 0000 to 1111 and then changes back to 0000

- Down counter counts from 1111 to 0000 and then back to 1111

- Counter counts up or down each clock cycle

- Output changes occur on clock rising edge

Fig. 6-13 4-Bit Up-Down Binary Counter

#### **Up/Down Synchronous Counters**

- Up/down synchronous counter: a bidirectional counter that is capable of counting either up or down.

- An input (control) line *UplDown* (or simply *Up*) specifies the direction of counting.

- ❖ Up/Down = 1 → Count upward

- $\div Up/Down = 0$  → Count downward

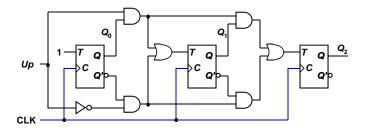

### **Up/Down Synchronous Counters**

Example: A 3-bit up/down synchronous binary counter.

| Clock pulse | Up       | $Q_2$ | $Q_1$ | $Q_0$ | Down     |

|-------------|----------|-------|-------|-------|----------|

| 0           | [₹       | 0     | 0     | 0     | -√-      |

| 1           |          | 0     | 0     | 1     | ≼        |

| 2           | >        | 0     | 1     | 0     | ≼        |

| 3           | <u>~</u> | 0     | 1     | 1     | ≼        |

| 4           | <u> </u> | 1     | 0     | 0     | ≼        |

| 5           | <u>~</u> | 1     | 0     | 1     | <b>4</b> |

| 6           | <u>~</u> | 1     | 1     | 0     | ∠        |

| 7           | <u>_</u> | 1     | 1     | 1     | 74       |

$$TQ_0 = 1$$

$TQ_1 = (Q_0.Up) + (Q_0'.Up')$

$TQ_2 = (Q_0.Q_1.Up) + (Q_0'.Q_1'.Up')$

### **Up/Down Synchronous Counters**

■ Example: A 3-bit up/down synchronous binary counter (cont'd).

$$TQ_0 = 1$$

$TQ_1 = (Q_0.Up) + (Q_0'.Up')$

$TQ_2 = (Q_0.Q_1.Up) + (Q_0'.Q_1'.Up')$

#### **Designing**

- As Covered Earlier

- Example: A 3-bit Gray code counter (using JK flip-flops).

|       | Present state |       |         | Next<br>state |         |        | Flip-flop<br>inputs |                 |     | Flip-flop<br>inputs |        |  |

|-------|---------------|-------|---------|---------------|---------|--------|---------------------|-----------------|-----|---------------------|--------|--|

| $Q_2$ | $Q_1$         | $Q_0$ | $Q_2^+$ | $Q_1^+$       | $Q_0^+$ | $JQ_2$ | KQ <sub>2</sub>     | JQ <sub>1</sub> | KQ₁ | $JQ_0$              | $KQ_0$ |  |

| 0     | 0             | 0     | 0       | 0             | 1       | 0      | X                   | 0               | Χ   | 1                   | X      |  |

| 0     | 0             | 1     | 0       | 1             | 1       | 0      | X                   | 1               | X   | X                   | 0      |  |

| 0     | 1             | 0     | 1       | 1             | 0       | 1      | X                   | X               | 0   | 0                   | X      |  |

| 0     | 1             | 1     | 0       | 1             | 0       | 0      | X                   | X               | 0   | X                   | 1      |  |

| 1     | 0             | 0     | 0       | 0             | 0       | X      | 1                   | 0               | X   | 0                   | X      |  |

| 1     | 0             | 1     | 1       | 0             | 0       | X      | 0                   | 0               | X   | X                   | 1      |  |

| 1     | 1             | 0     | 1       | 1             | 1       | X      | 0                   | Χ               | 0   | 1                   | X      |  |

| 1     | 1             | 1     | 1       | 0             | 1       | X      | 0                   | Χ               | 1   | X                   | 0      |  |

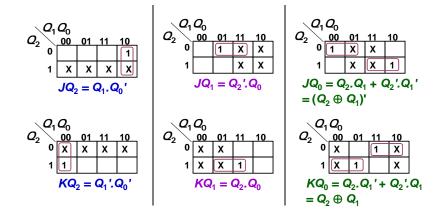

## **Up/Down Synchronous Counters**

■ 3-bit Gray code counter: flip-flop inputs.

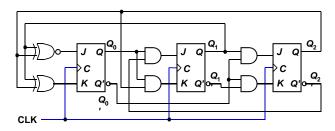

#### **Up/Down Synchronous Counters**

■ 3-bit Gray code counter: logic diagram.

$$\begin{array}{ll} JQ_2 = Q_1.Q_0' & JQ_1 = Q_2'.Q_0 & JQ_0 = (Q_2 \oplus Q_1)' \\ KQ_2 = Q_1'.Q_0' & KQ_1 = Q_2.Q_0 & KQ_0 = Q_2 \oplus Q_1 \end{array}$$

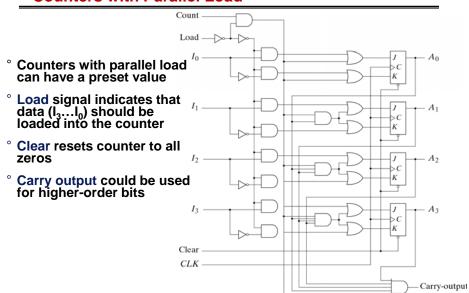

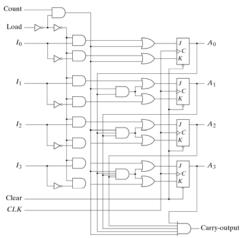

#### **Counters with Parallel Load**

Fig. 6-14 4-Bit Binary Counter with Parallel Load

#### **Counters with Parallel Load**

| Clear | Clk      | Load | Count | Function    |

|-------|----------|------|-------|-------------|

| 0     | X        | X    | X     | Clear to 0  |

| 1     | <b>↑</b> | 1    | X     | Load inputs |

| 1     | <b>↑</b> | 0    | 1     | Count       |

| 1     | <b>↑</b> | 0    | 0     | No Change   |

#### **Function Table**

- ° If Clear is asserted (0), the counter is cleared

- If Load is asserted data inputs are loaded

- If Count asserted counter value is incremented

Fig. 6-14 4-Bit Binary Counter with Parallel Load

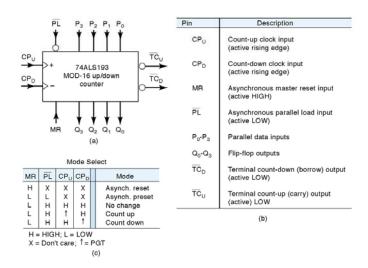

### **Binary Counter with Parallel Load and Preset**

· Commercial version of binary counter

#### **Summary**

- ° Binary counters can be ripple or synchronous

- ° Ripple counters use flip flop outputs as flop triggers

- · Some delay before all flops settle on a final value

- · Do no require a clock signal

- ° Synchronous counters are controlled by a clock

- · All flip flops change at the same time

- Up/Down counters can either increment or decrement a stored binary value

- · Control signal determines if counter counts up or down

- ° Counters with parallel load can be set to a known value before counting begins.