Indian Institute of Technology Jodhpur, Year 2018

#### **Analog Electronics**

(Course Code: EE314)

# Lecture 9-10: BJT Small Signal, Biasing, Amplifiers

#### Course Instructor: Shree Prakash Tiwari

Email: <a href="mailto:sptiwari@iitj.ac.in">sptiwari@iitj.ac.in</a>

Webpage: <a href="http://home.iitj.ac.in/~sptiwari/">http://home.iitj.ac.in/~sptiwari/</a>

Course related documents will be uploaded on <a href="http://home.iitj.ac.in/~sptiwari/EE314/">http://home.iitj.ac.in/~sptiwari/EE314/</a>

**Note:** The information provided in the slides are taken form text books for microelectronics (including Sedra & Smith, B. Razavi), and various other resources from internet, for **teaching/academic use only**

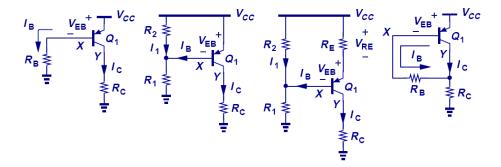

# **PNP BJT Biasing**

Note that the emitter is biased at a higher potential than the base and the collector.

# **Small-Signal Analysis**

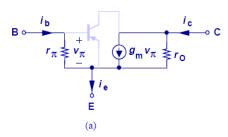

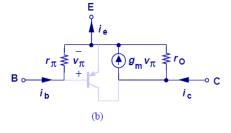

# PNP BJT Small-Signal Model

- The small-signal model for a PNP transistor is identical to that of an NPN transistor.

- Note that the polarity of the small-signal currents and voltages are defined to be in the opposite direction with respect to the large-signal model. This is OK, because the small-signal model is used only to determine *changes* in currents and voltages.

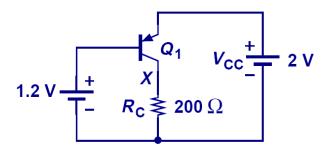

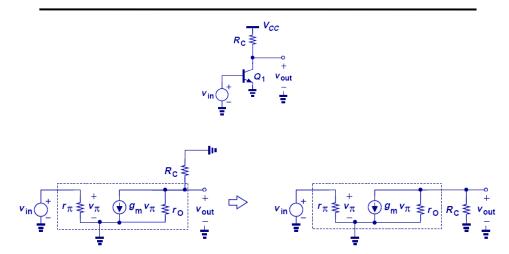

# Small-Signal Model Example 1

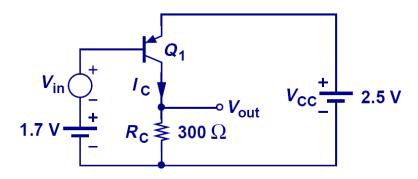

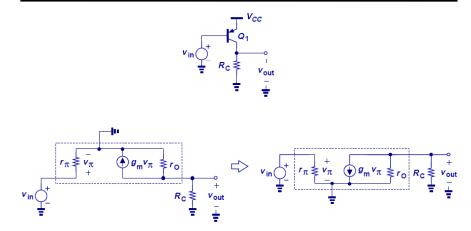

# Small-Signal Model Example 2

• Note that the small-signal model is identical to that in the previous example.

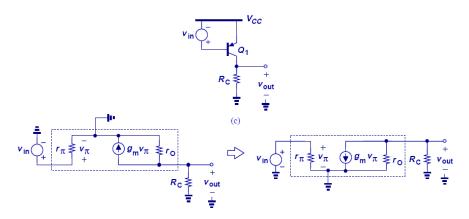

# Small-Signal Model Example 3

• Note that the small-signal model is identical to that in the previous examples.

# BJT Amplifiers: Overview

#### **General Concepts**

- Input and Output Impedances

- Biasing

- DC and Small-Signal Analysis

#### **Operating Point Analysis**

- Simple Biasing

- Emitter Degeneration

- Self-Biasing

- Biasing of PNP Devices

#### **Amplifier Topologies**

- Common-Emitter Stage

- Common-Base Stage

- Emtter Follower

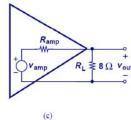

# Voltage Amplifier

- In an ideal voltage amplifier, the input impedance is infinite and the output impedance is zero.

- In reality, the input and output impedances depart from their ideal values.

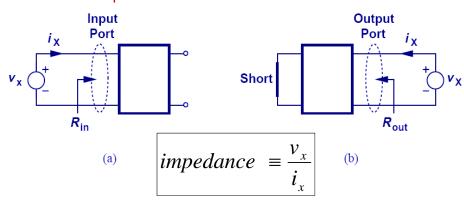

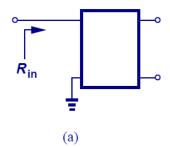

# Input/Output Impedances

- The figures below show how input and output impedances are determined.

- All independent sources are set to zero.

#### Input Impedance Example

- Note that input/output impedances are usually regarded as small-signal quantities.

- The input impedance is obtained by applying a small change in the input voltage and finding the resultant change in the input current:

# Impedance at a Node

When calculating I/O impedances at a port, we usually ground one terminal. We often refer to the "impedance seen at a node" rather than the impedance between two nodes (i.e. at a port).

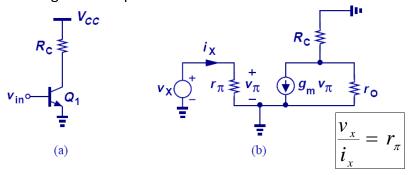

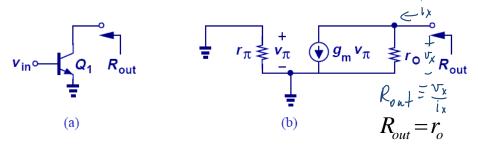

#### Impedance seen at the Collector

• The impedance seen at the collector is equal to the intrinsic output impedance of the transistor, if the emitter is grounded.

#### Impedance seen at the Collector

The impedance seen at the collector is equal to the intrinsic output impedance of the transistor, if the emitter is grounded.

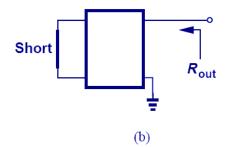

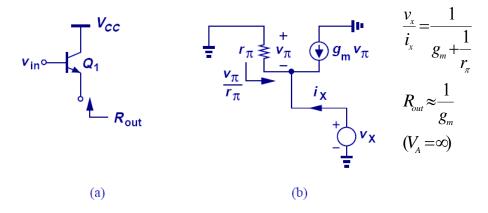

#### Impedance seen at the Emitter

The impedance seen at the emitter is approximately equal to the inverse of its transconductance, if the base is grounded.

#### Impedance seen at the Emitter

The impedance seen at the emitter is approximately equal to the inverse of its transconductance, if the base is grounded.

$$v_{\text{in}} \sim \begin{array}{c} V_{\text{cc}} \\ \hline \\ v_{\text{in}} \\ \hline \\ R_{\text{out}} \end{array} \qquad \begin{array}{c} V_{x} \\ \hline \\ v_{\pi} \\ \hline \\ r_{\pi} \\ \hline \end{array} \qquad \begin{array}{c} V_{x} \\ \hline \\ v_{\pi} \\ \hline \\ r_{\pi} \\ \hline \end{array} \qquad \begin{array}{c} V_{x} \\ \hline \\ v_{\pi} \\ \hline \\ v_{\pi} \\ \hline \\ v_{\chi} \\ v_{\chi} \\ \hline \\ v_{\chi} \\ v_{\chi} \\ \hline \\ v_{\chi} \\ v_{\chi}$$

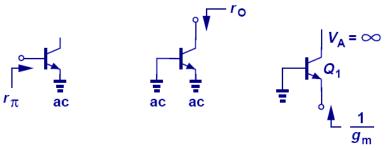

#### **Summary of BJT Impedances**

- 1. Looking into the base, the impedance is  $r_{\pi}$  if the emitter is (ac) grounded.

- 2. Looking into the collector, the impedance is  $r_0$  if emitter is (ac) grounded.

- 3. Looking into the emitter, the impedance is  $1/g_{\rm m}$  if base is (ac) grounded and Early effect is neglected.

# Biasing of BJT

- Transistors must be biased because

- 1. They must operate in the active region, and

- 2. Their small-signal model parameters are set by the bias conditions.

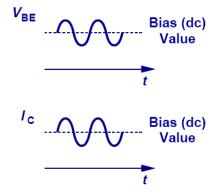

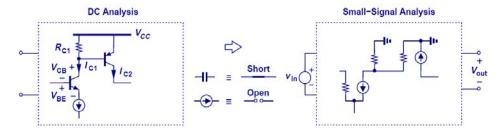

# DC Analysis vs. Small-Signal Analysis

- Firstly, DC analysis is performed to determine the operating point and to obtain the small-signal model parameters.

- Secondly, independent sources are set to zero and the small-signal model is used.

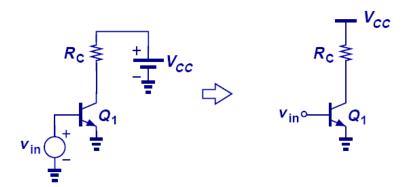

### **Simplified Notation**

• Hereafter, the voltage source that supplies power to the circuit is replaced by a horizontal bar labeled  $V_{\rm CC}$ , and input signal is simplified as one node labeled  $v_{\rm in}$ .

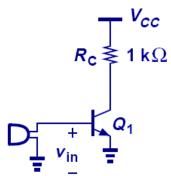

#### **Example of Bad Biasing**

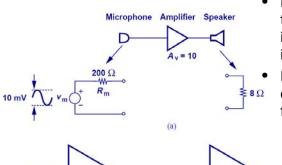

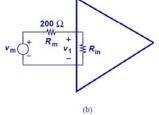

- The microphone is connected to the amplifier in an attempt to amplify the small output signal of the microphone.

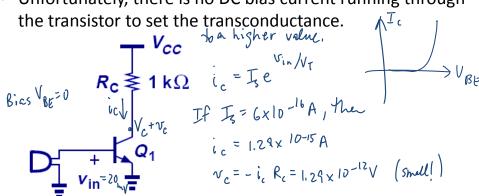

- Unfortunately, there is no DC bias current running through the transistor to set the transconductance.

### **Example of Bad Biasing**

• The microphone is connected to the amplifier in an attempt to amplify the small output signal of the microphone.

Unfortunately, there is no DC bias current running through

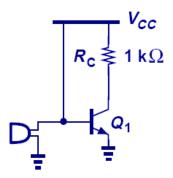

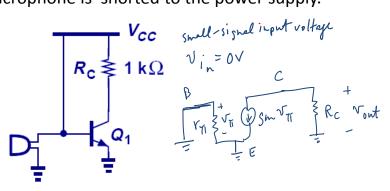

#### **Another Example of Bad Biasing**

- The base of the amplifier is connected to  $V_{\rm CC}$ , trying to establish a DC bias.

- Unfortunately, the output signal produced by the microphone is shorted to the power supply.

#### **Another Example of Bad Biasing**

- The base of the amplifier is connected to  $V_{\rm CC}$ , trying to establish a DC bias.

- Unfortunately, the output signal produced by the microphone is shorted to the power supply.

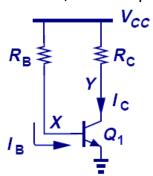

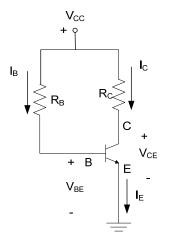

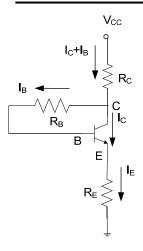

#### Biasing with Base Resistor

- Assuming a constant value for  $V_{\rm BE}$ , one can solve for both  $I_{\rm B}$  and  $I_{\rm C}$  and determine the terminal voltages of the transistor.

- However, the bias point is sensitive to  $\beta$  variations.

# Biasing with Base Resistor

Using KVL in the base-emitter loop,

$$V_{CC} - I_B R_B - V_{BE} = 0$$

or,  $I_B = (V_{CC} - V_{BE})/R_B$

$$I_C = \beta I_B = \beta (V_{CC} - V_{BE})/R_B$$

Using KVL in the collector-emitter loop,

$$V_{CC} - I_C R_C - V_{CE} = 0$$

or,  $V_{CE} = V_{CC} - I_C R_C$

$Q(V_{CE},I_{C})$  is set

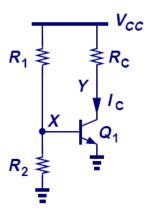

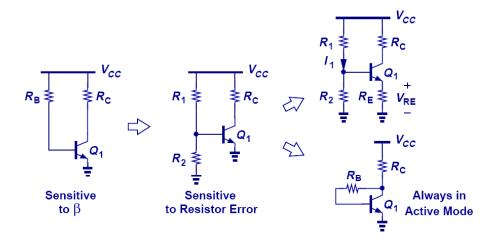

#### Improved Biasing: Resistive Divider

• Using a resistive divider to set  $V_{\rm BE}$ , it is possible to produce an  $I_{\rm C}$  that is relatively insensitive to variations in  $\beta$ , if the base current is small.

### **Accounting for Base Current**

• With a proper ratio of  $R_1$  to  $R_2$ ,  $I_C$  can be relatively insensitive to  $\beta$ . However, its exponential dependence on  $R_1$  //  $R_2$  makes it less useful.

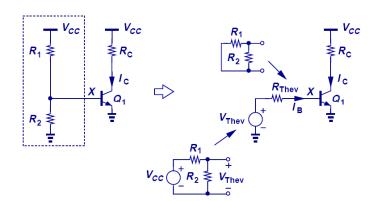

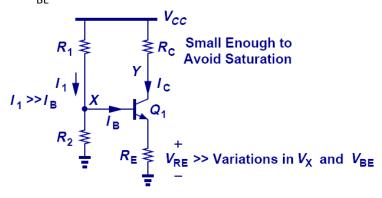

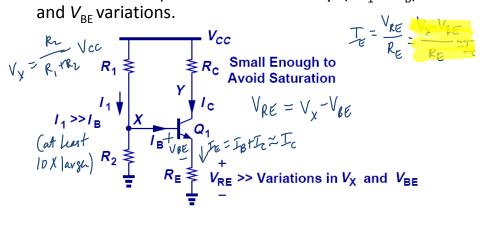

#### **Emitter Degeneration Biasing**

- $R_{\rm F}$  helps to absorb the change in  $V_{\rm X}$  so that  $V_{\rm BF}$  stays relatively constant.

- This bias technique is less sensitive to  $\beta$  (if  $I_1 >> I_B$ ) and  $V_{\rm BE}$  variations.

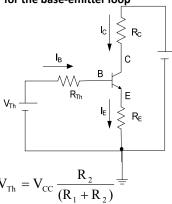

### **Emitter Degeneration Biasing**

Thevenin's Equivalent Circuit for the base-emitter loop

$$R_{Th} = R_1 || R_2 = \frac{R_1 R_2}{(R_1 + R_2)}$$

**Base-Emitter Loop**

Base-Emitter Loop

$$V_{Th} - I_{B}R_{Th} - V_{BE} - (\beta + 1)I_{B}R_{E} = 0$$

or,

$$I_{B} = \frac{V_{Th} - V_{BE}}{R_{Th} + (\beta + 1)R_{E}}$$

$$Collector-Emitter Loop$$

$$I_{C} = \beta I_{P} = \frac{\beta(V_{Th} - V_{BE})}{\beta(V_{Th} - V_{BE})}$$

$$I_{C} = \beta I_{B} = \frac{\beta (V_{Th} - V_{BE})}{R_{Th} + (\beta + 1)R_{E}}$$

$$V_{CE} = V_{CC} - I_{C}R_{C} - I_{E}R_{E} = V_{CC} - I_{C}R_{C} - (I_{C} + I_{B})R_{E}$$

### **Emitter Degeneration Biasing**

#### **Bias Stabilization**

$$\begin{split} I_{C} &= \frac{\beta(V_{Th} - V_{BE})}{R_{Th} + (\beta + 1)R_{E}} & \left[ V_{Th} = V_{CC} \, \frac{R_{2}}{(R_{1} + R_{2})} \right] \\ \text{If R}_{Th} &<< (\beta + 1)R_{E} \text{, then} & \left[ R_{Th} = R_{1} \middle\| R_{2} = \frac{R_{1}R_{2}}{(R_{1} + R_{2})} \right] \\ I_{C} &\approx \frac{V_{Th} - V_{BE}}{R_{E}} \end{split}$$

So,  $I_C$  is independent of  $\beta$

### **Emitter Degeneration Biasing**

- $R_F$  helps to absorb the change in  $V_X$  so that  $V_{BE}$  stays relatively constant.

- This bias technique is less sensitive to  $\beta$  (if  $I_1 >> I_B$ ) and  $V_{\rm BE}$  variations.

#### **Bias Circuit Design Procedure**

1. Choose a value of  $I_C$  to provide the desired smallsignal model parameters:  $g_{\rm m}$ ,  $r_{\pi}$ , etc.

- $\Im_{m} = \frac{\mathcal{F}_{m}}{V_{*}} \mathcal{F}_{m} = \frac{\mathcal{F}_{m}}{\mathcal{F}_{m}}$ 2. Considering the variations in  $R_{1}$ ,  $R_{2}$ , and  $V_{BE}$ , choose a value for V<sub>RE.</sub> V<sub>RE</sub> ~ IcRE , e.s. 200 mV = dolumine

- 3. With  $V_{\rm RE}$  chosen, and  $V_{\rm BE}$  calculated,  $V_{\rm x}$  can be determined.  $V_{BE} = V_{T} h_{T} = V_{X} = V_{RE} + V_{BE}$

- 4. Select  $R_1$  and  $R_2$  to provide  $V_x$ .  $V_y = \frac{k_1}{R_1 T R_1} V_{cc}$ and I >> IB 5. Choose Rc to guarantee active mode operation.

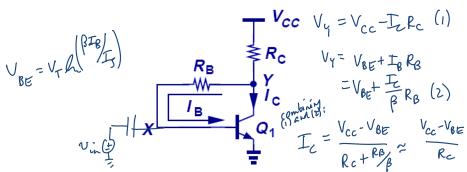

# Self-Biasing Technique

- This bias technique utilizes the collector voltage to provide the necessary  $V_{\nu}$  and  $I_{\rm R}$ .

- One important characteristic of this approach is that the collector has a higher potential than the base, thus guaranteeing active-mode operation of the BJT.

# Self-Biasing Design Guidelines

$$(1) R_C >> \frac{R_B}{\beta}$$

$$(2) \Delta V_{BE} << V_{CC} - V_{BE}$$

- (1) provides insensitivity to  $\beta$ .

- (2) provides insensitivity to variation in  $V_{\mathrm{BE}\,.}$

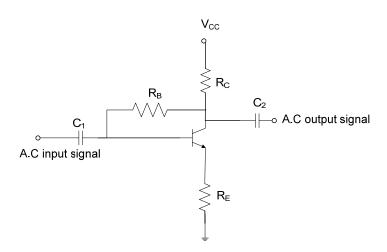

#### **Emitter and Collector Feedback Bias**

#### **Emitter and Collector Feedback Bias**

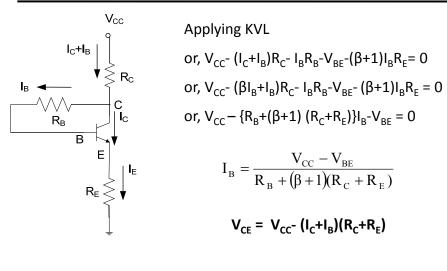

Applying KVL

or,

$$V_{CC}^{-}(I_C + I_B)R_{C}^{-}I_BR_{B}^{-}V_{BF}^{-}(\beta + 1)I_BR_F^{-} = 0$$

or,

$$V_{CC}^{-} (\beta I_B + I_B) R_{C}^{-} I_B R_B - V_{BE}^{-} (\beta + 1) I_B R_E = C$$

or,

$$V_{CC} - \{R_B + (\beta + 1) (R_C + R_E)\}I_B - V_{BE} = 0$$

$$I_{_{B}} = \frac{V_{_{CC}} - V_{_{BE}}}{R_{_{B}} + (\beta + 1)(R_{_{C}} + R_{_{E}})}$$

$$V_{CE} = V_{CC} - (I_C + I_B)(R_C + R_E)$$

#### **Emitter and Collector Feedback Bias**

$$I_{C} = \frac{(V_{CC} - V_{BE})\beta}{R_{B} + (\beta + 1)(R_{C} + R_{E})}$$

$$V_{CE} = V_{CC} - (I_C + I_B)(R_C + R_E)$$

Bias Stabilization

**Bias Stabilization**

If  $R_B << (\beta+1)(R_C + R_E)$ , then

or,

$$I_C \approx \frac{(V_{CC} - V_{BE})}{(R_C + R_E)}$$

So,  $I_c$  is independent of  $\beta$

# **Summary of Biasing Techniques**

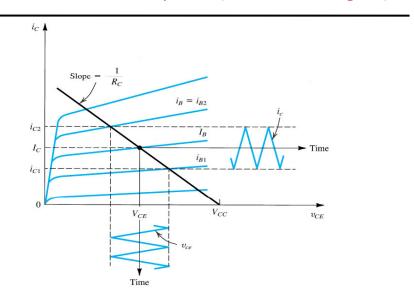

#### Transistor as an Amplifier (ac in active region)

# **PNP BJT Biasing Techniques**

• The same principles that apply to NPN BJT biasing also apply to PNP BJT biasing, with only voltage and current polarity modifications.